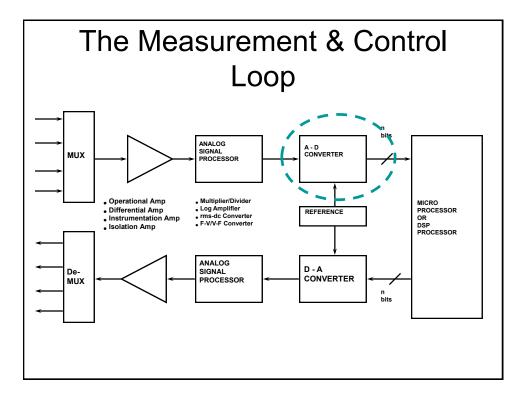

# Outline • Digital Signal Processing: • Sampling; • Sample and Hold; • Analog to Digital Conversion; • Digital to Analog Conversion.

# Sampling & Quantization For every system there is an appropriate sampling rate and degree of quantization (resolution) so that the system retains as much information as it needs about the input signals Ultimately, the purpose of sampling and quantization is to reduce as much as possible the amount of information about a signal that a system must store in order to reconstruct or analyze it meaningfully.

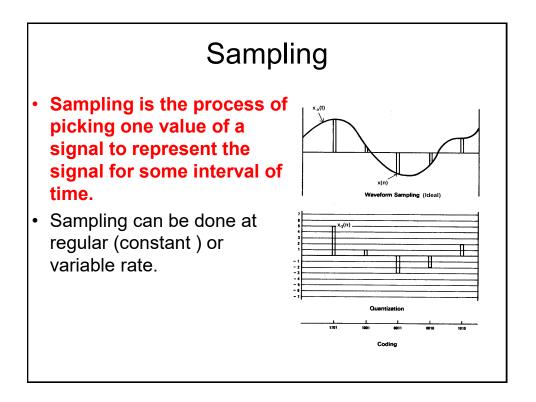

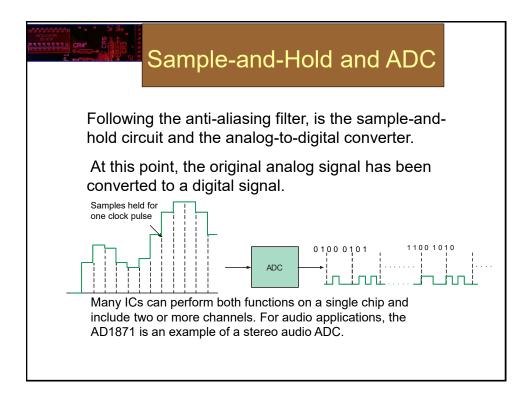

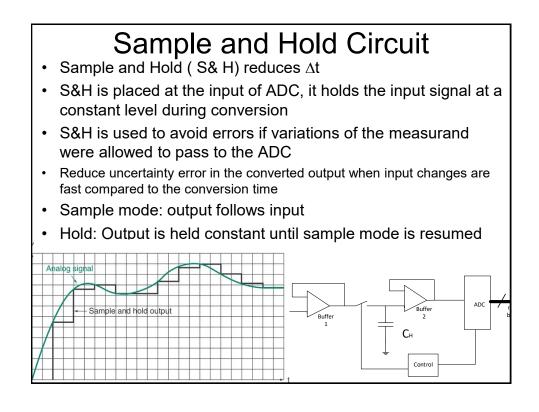

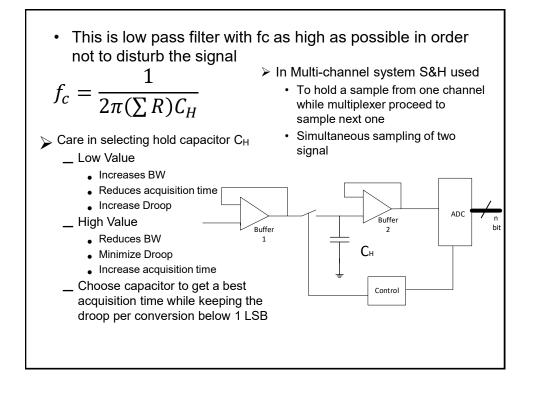

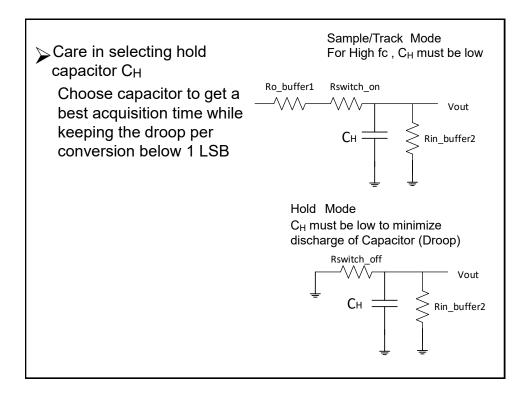

- Sampling is done by a circuit called a *sample-and-hold (S/H)*, which, at a sampling instant, transfers the input signal to the output and holds it steady, even though the input signal may still be changing.

- Most modern ADC chip has a built-in S/H or T/H, and virtually all data acquisition systems include them.

- Of course, sampling necessarily throws away some information, so the art of sampling is in choosing the right sample rate so that enough of the input signal is preserved.

# Minimum sampling rate (Nyquest Rate)

• Nyquest criterion states that the sampling rate must be at least twice the highest frequency of the signal of interest:

#### fsampling > 2f signal

- Nyquest criterion guarantees the preservation of the frequency content of the signal, but not the time dependency

- In order to be able to reconstruct the signal in time domain, as a rule of thump, we use : fsampling > 10\*fsignal

- Aliasing occurs when the sampling is done at a rate less than Nyquest rate

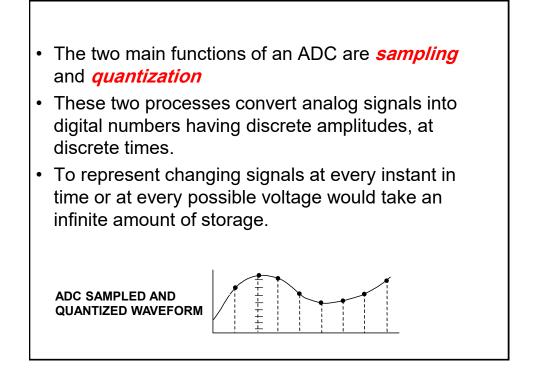

# Quantization

- Quantization is the second step in ADC in which the samples are converted into equivalent digital value

- What sampling accomplishes in the time domain, quantization does in the amplitude domain

- Conversion takes finite time , and next sample cannot be taken before the last sample conversion is completed.

- The smaller the intervals between the samples, the higher the sampling rate (sampling frequency)

# Quantization

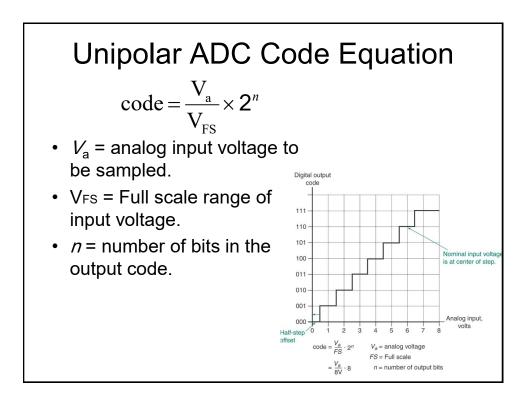

- An ADC quantizes a sampled signal by picking one integer value from a predetermined, finite list of integer values to represent each analog sample.

- Each integer value in the list represents a fraction of the total analog input range.

- Normally, an ADC chooses the value closest to the actual sample from a list of uniformly spaced values.

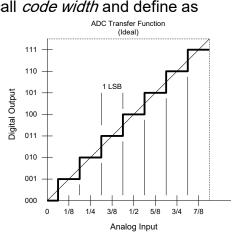

- This rule gives the *transfer function* of analog input to- digital output a uniform "staircase" characteristic.

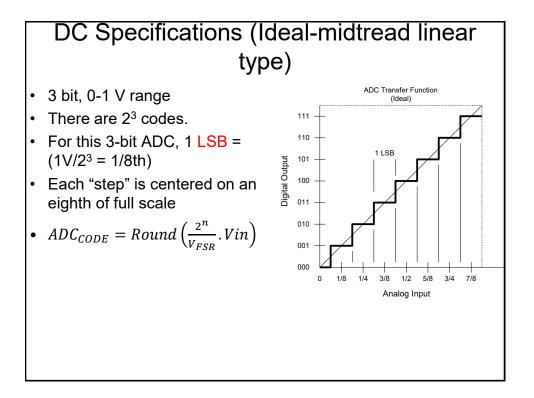

- Figure represents a three-bit quantizer, which maps a continuum of analog input values to only eight (2^3) possible output values.

- Each step in the staircase has (ideally) the same width along the *x*-axis, which we call *code width* and define as 1*LSB (least significant bit)*

- In this case 1 LSB is equal to 1/8 V. Each digital code corresponds to one of eight 1-LSB intervals making up the analog input range, which is 8 LSB (and also 1 V in this case).

# ADC Specifications

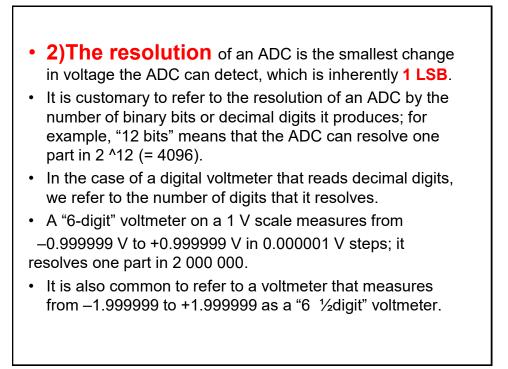

- 1. Range: The input range of ADC is the span of voltage over which the ADC can make conversion

- The end points at the bottom and the top of the range are called –*full-scale* and + *full-scale*, respectively.

- When -full-scale = 0 V the range is called *unipolar*

- when –full-scale is a negative voltage of the same magnitude as +full-scale the range is said to be *bipolar*

- When the input voltage exceeds the input range, the conversion data are certain to be wrong, and most ADCs report the code at the end point of the range closest to the input voltage.

- This condition is called an over-range

Example : 8 bit ADC with a range 0-2.5 V input

$$\Delta = LSB = Q = \frac{2.5}{2^8} = \frac{2500mV}{256} = 9.765 \text{ mV}$$

Or as %

$$\Delta = \frac{9.765}{2500} * 100\% = 0.3906\%$$

Or 0.003906 → 3906 ppm (parts per million)

#### ADC Resolution vs. Quantization Parameters

| Resolution,<br>Bits (n)                              | 2 <sup>n</sup> | LSB, mV<br>(2.5V FS) | %<br>Full Scale | ppm<br>Full Scale | dB<br>Full Scale |  |  |  |

|------------------------------------------------------|----------------|----------------------|-----------------|-------------------|------------------|--|--|--|

| 8                                                    | 256            | 9.77                 | 0.391           | 3906              | -48.0            |  |  |  |

| 10                                                   | 1024           | 2.44                 | 0.098           | 977               | -60.0            |  |  |  |

| 12                                                   | 4096           | 0.610                | 0.024           | 244               | -72.0            |  |  |  |

| 14                                                   | 16,384         | 0.153                | 0.006           | 61                | -84.0            |  |  |  |

| 16                                                   | 65,536         | 0.038                | 0.0015          | 15                | -96.0            |  |  |  |

| 18                                                   | 262,164        | 0.0095               | 0.00038         | 3.8               | -108.0           |  |  |  |

| <ul> <li>Higher n gives better resolution</li> </ul> |                |                      |                 |                   |                  |  |  |  |

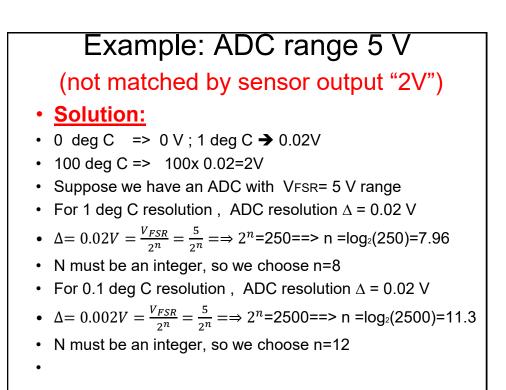

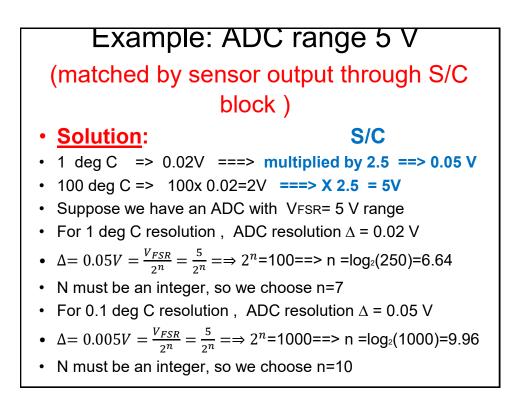

# Example

#### sensor output matched to ADC input

- + For 0.1 deg C resolution , ADC resolution  $\Delta$  = 0.002 V

- $\Delta = 0.002V = \frac{V_{FSR}}{2^n} = \frac{2}{2^n} \Longrightarrow 2^n = 1000 \Longrightarrow n = \log_2(1000) \Longrightarrow 9.97$

- N must be an integer, so we choose n=10

# Conclusion about range matching

- When the ranges are not matched, higher number of bits "n" is required to achieve higher measurement resolution

- When we match the output range of the sensor to the input range of ADC, we can get better resolution of a given ADC with given number of bits

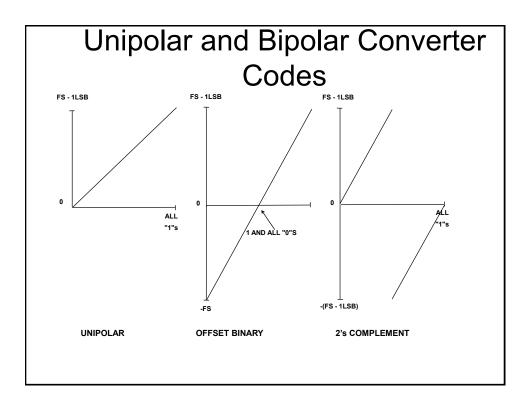

# **Coding Conventions**

- There are several different formats for ADC output data:

- Unipolar

- Bipolar

- An ADC using *binary* coding produces all 0s (e.g., 000 for the three-bit converter) at –full-scale and all 1s (e.g., 111) at +full-scale.

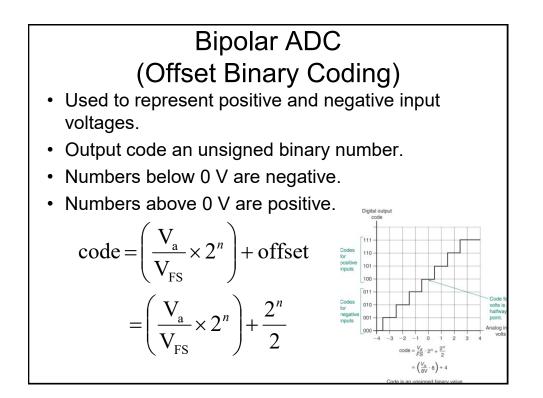

- If the range is bipolar, so that –full-scale is a negative voltage, binary coding is sometimes called *offset binary* since the code 0 does not refer to 0 V.

- To make digital 0 correspond to 0 V, bipolar ADCs use *two's* complement coding, which is identical to offset binary coding except that the most significant bit (MSB) is inverted, so that 100 ... 00 corresponds to –full-scale, 000 ... 00 corresponds to 0 V (*midscale*), and 011 ... 11 corresponds to +full-scale.

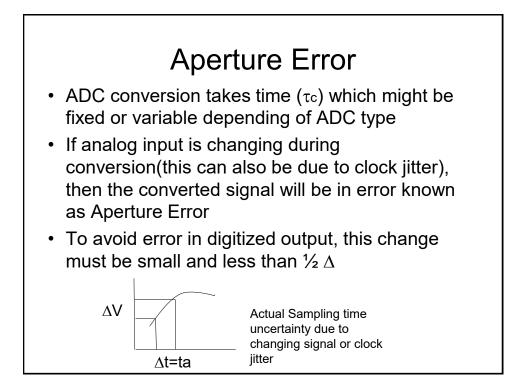

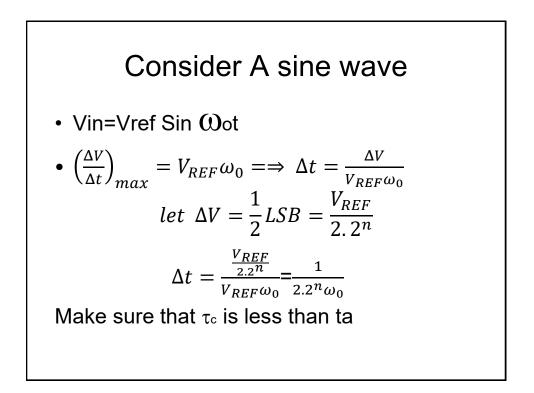

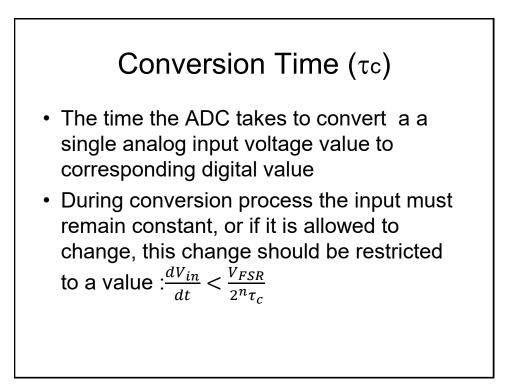

• 10 bit ADC with  $\tau_c=20 \ \mu s$ , what is the maximum allowable rate of change (frequency) of a sinusoidal input voltage to be converted using this ADC

• Solution:

$$\frac{dV_{in}}{dt} < \frac{V_{FSR}}{2^n \tau_c}$$

•

$$A\omega_o < \frac{V_{FSR}}{2^n \tau_c}$$

, let  $A = V_{FSR}$

$\omega_o < \frac{1}{2^n \tau_c}$

$$f_o < \frac{1}{2\pi . 2^{10} 20\mu s} = 7.75 \ Hz$$

This is the maximum frequency of input to be used with this ADC>>>> If higher frequency needed , increase n or reduce  $\tau_c$

# Converter Throughput Rate/ Frequency

- It is defined as the number of times the input signal can be sampled maintaining full accuracy

- It is calculated as the inverse of total time required for one successful conversion

- 1) For ADC's without S&H

$$f = throughput = \frac{1}{\tau_c}$$

• 2) For ADC's with S&H: other delays affect the throughput

$$f = throughput = \frac{1}{\sum \tau}$$

where

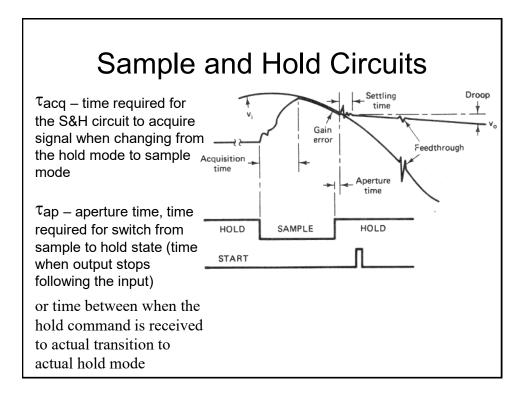

$\sum \tau = \tau_c + \tau_{acq} + \tau_{ap}$

# Types of ADCs

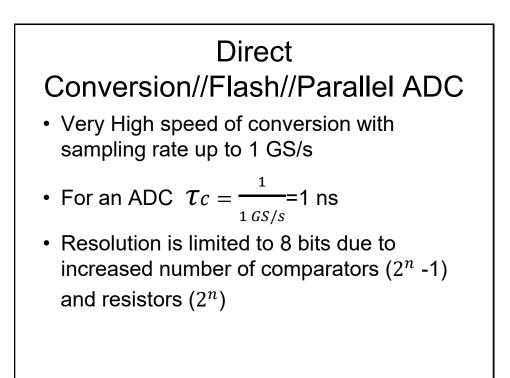

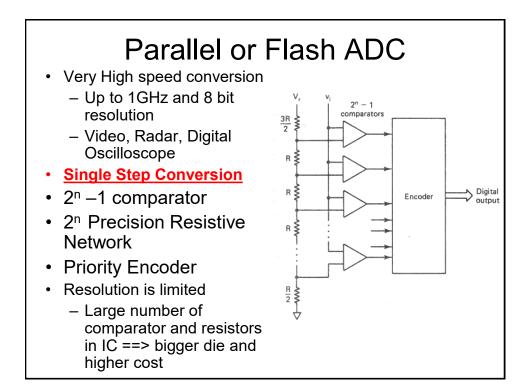

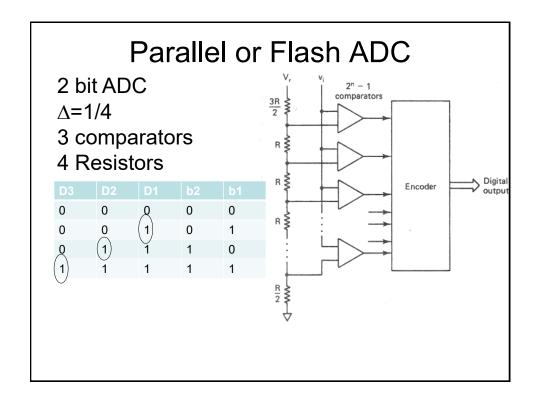

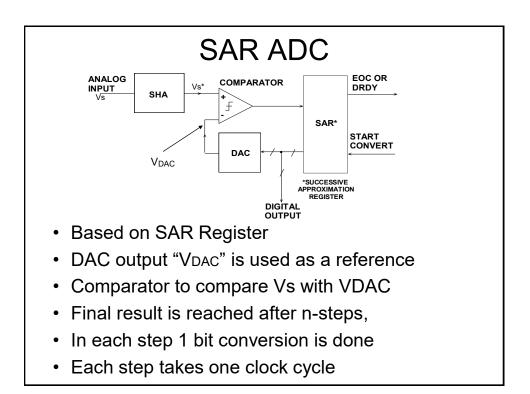

- Most ADC types have the following two blocks in common:

- Comparator ==> Vo= logic "1" if V(+) > V(-)

- i.e. comparator is a 1 bit ADC

- Precise and stable voltage reference

# Example

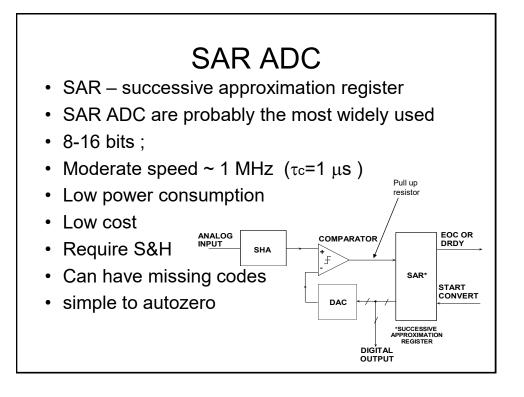

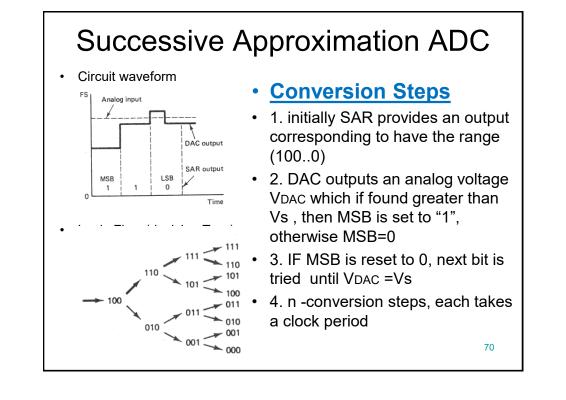

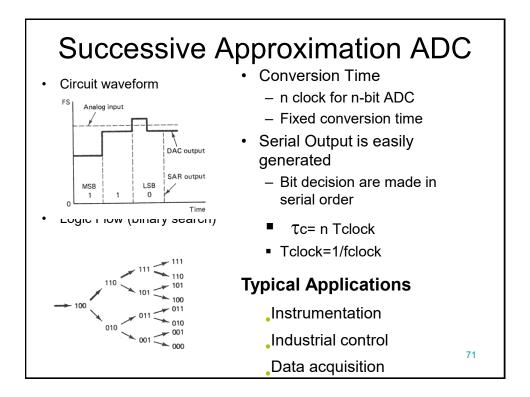

- VFSR=5V, 4 bit, SAR ADC, Vs=Vin=3.127 V, explain how conversion is done?

- Solution:

- Suppose Output is b1b2b3b4

- (1) let b1=1, b2=b3=b4=0

- 1000 ==> VDAC=8/2^4\*VREF=2.5V

- Check VDAC > Vs ? (2.5 > 3.127? ==> NO ==> set b1=1

- (2) set b2=1, b3=b4=0

- 1100 ==> VDAC=10/2^4\*VREF=3.75V

- Check VDAC > Vs ? (3.75 > 3.127? ==> Yes ==> Reset b2=0

- (3) set b3=1, b4=0

- 1010 ==> VDAC=10/2^4\*VREF=3.1255V

- Check VDAC > Vs ? (3.125 > 3.127? ==> No ==> set b3=1

- (4) set b4=1, 1011 ==> VDAC=11/2<sup>4</sup>\*VREF=3.4375V

- Check VDAC > Vs ? (3.4375 > 3.127? ==> Yes ==> Reset b4=0

- Final Result: 1010

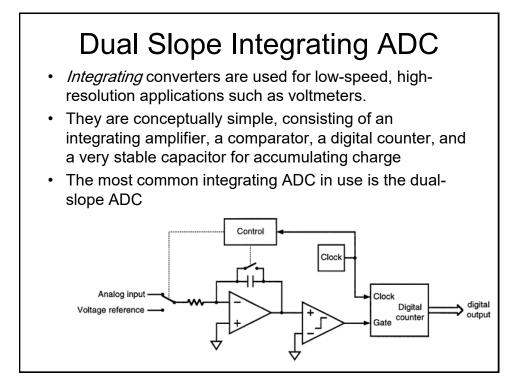

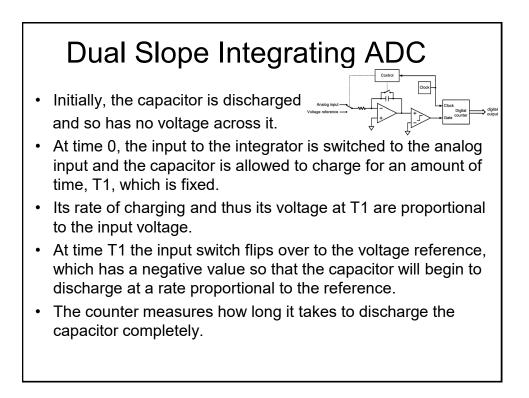

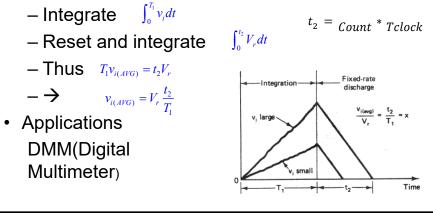

- If the capacitor is of high quality, the ratio of the discharge time to the charge time is proportional to the ratio of the input voltage to the voltage reference, and so the counter output represents the analog input voltage.

- t2/T1=Vi(avg)/VREF

- Operation

- Integrating converters do not sample the voltage itself; they *average* the voltage over the integration period and *then* they sample the average that is accumulated on the capacitor.

- This tends to reject noise that conventional sampling cannot, especially periodic noises. Most integrating ADCs operate with an integration period that is a multiple of one AC line period (1/60 or 1/50 s) so that any potential interference from stray electric or magnetic fields caused by the power system is canceled.

- Low speed

- High resolution and low cost

- Very stable

- Excellent Noise Rejection

- High frequency noise cancelled out b

- Proper T<sub>1</sub> eliminates line noise

- Easy to obtain good resolution

| ADC Comparison                       |                  |                 |                 |                    |                 |  |  |  |  |

|--------------------------------------|------------------|-----------------|-----------------|--------------------|-----------------|--|--|--|--|

| Characteristic                       | Flash            | Pipeline        | SAR             | Sigma-<br>Delta    | Integrating     |  |  |  |  |

| Throughput<br>Samples/sec            | 1                | 2               | 3               | 4                  | 5               |  |  |  |  |

| Resolution                           | 5                | 3               | 4               | 2                  | 1               |  |  |  |  |

| Latency<br>Sample to<br>output<br>Tc | 1                | 3               | 2               | 4                  | 5               |  |  |  |  |

| Power<br>consumption                 | Constant<br>High | Constant<br>Low | Variable<br>Low | Constant<br>Medium | Constant<br>Low |  |  |  |  |

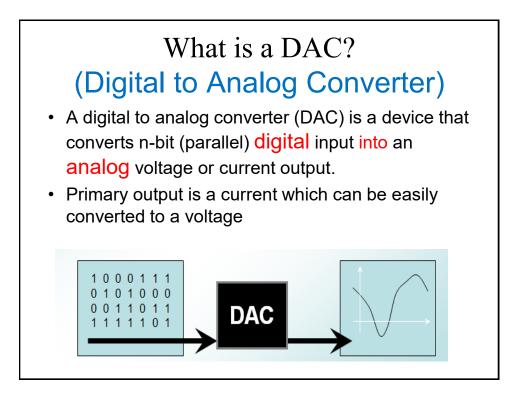

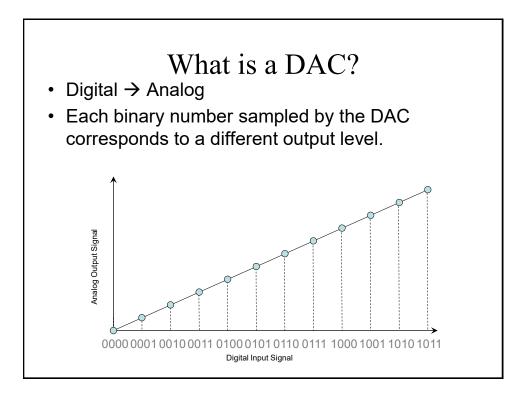

# END ADC ==> ==> START DAC

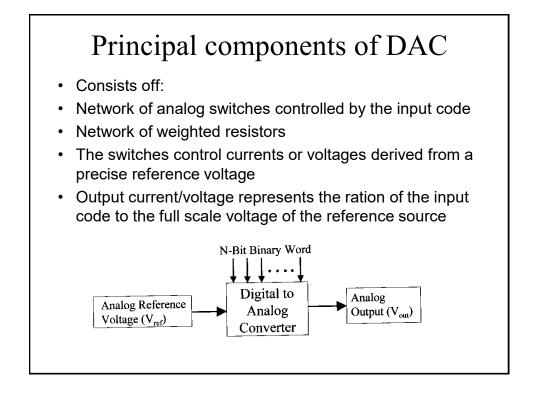

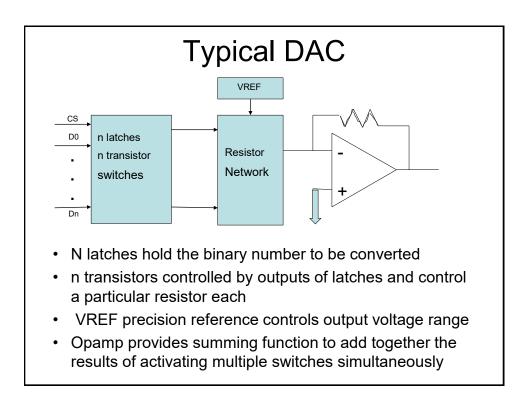

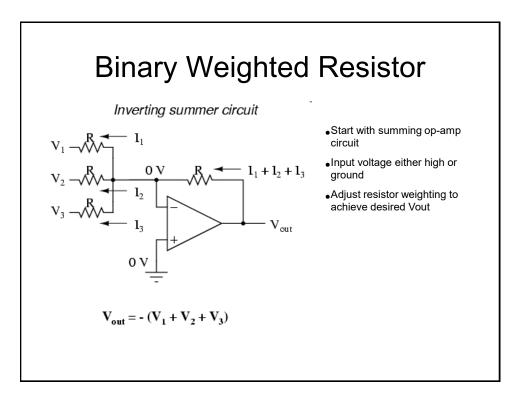

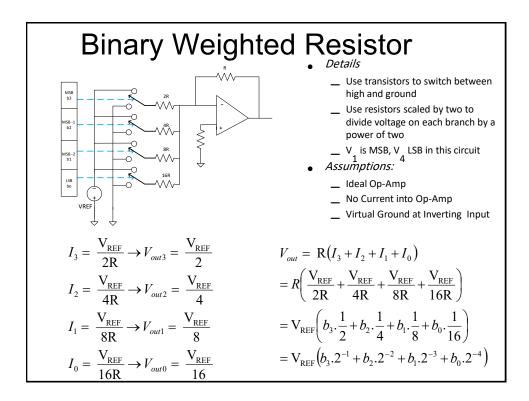

# Types of DAC implementations

- Binary Weighted Resistor

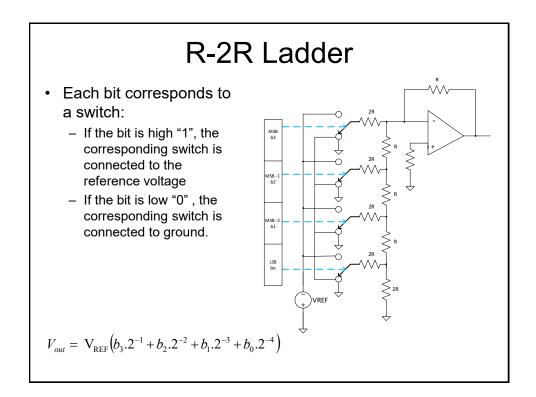

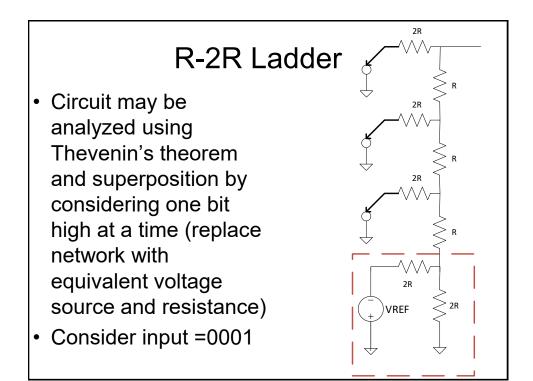

- R-2R Ladder

Ken Marek

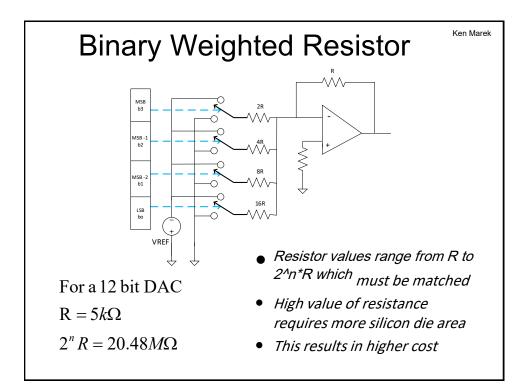

# **Binary Weighted Resistor**

- Advantages

- Simple

- Fast

- Disadvantages

- Need large range of resistor values (2048:1 for 12-bit) with high precision in low resistor values

- Need very small switch resistances

- Op-amp may have trouble producing low currents at the low range of a high precision DAC

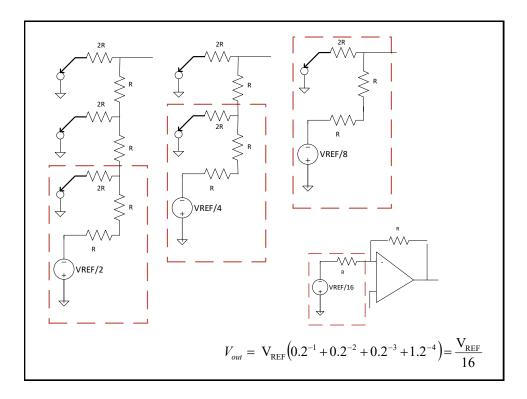

- Contribution of each input bit can be found in a similar fashion, by setting its value to 1 while all other bits are set to zero

- R-2R DAC resistor values are limited to two values only R or 2R which is less expensive

- Number of resistors is less: 2n+1 and lower precision is acceptable

- · Conversion speed is lower

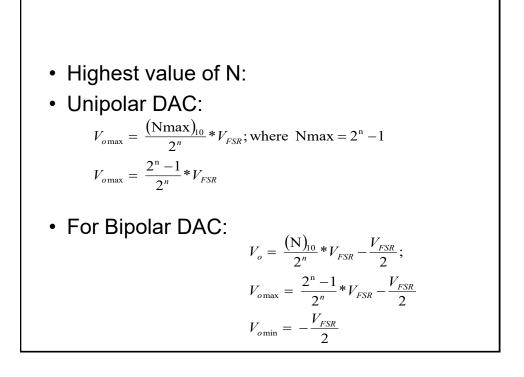

- Example: an 8 bit DAC with 5V reference has an input 10100111, what is the output?

$$V_{out} = \frac{167}{256} * 5 = 3.2617 \,\mathrm{V}$$

• Example: a 10 bit DAC with 10V reference, what input is required to get 6.5V output?

$$V_{out} = \frac{(N)_{10}}{2^{10}} * 10 = 6.5 V$$

(N)<sub>10</sub> =  $\frac{6.5 * 2^{10}}{10} = 665.6$

if N =  $665 = > V = 6.494$

if N =  $666 = > V = 6.504$  (closer to required value)

# Examples

- A bipolar 10 bit DAC has V<sub>FSR</sub>=5V and a hexadecimal input 2A4, what is the output? And at what input the output will be zero?

- Solution: 2A4 = 10 1010 0100 ==> (512+128+32+4)<sub>10</sub>=676<sub>10</sub>

$$V_o = \frac{676}{1024} * 5 - \frac{5}{2} = -0.8$$

• For Vo=0

$$0 = \frac{(N)_{10}}{1024} * 5 - \frac{5}{2} ==>$$

N = 512

0010 0000 0000 ==> (200)<sub>H</sub>

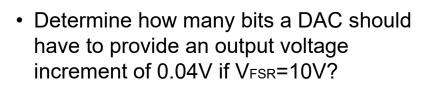

V

$$\Delta = \frac{V_{FSR}}{2^n} = 0.04$$

$$2^n = \frac{10}{0.04} = 250$$

$$n \ln n = \ln 250$$

$$n = \frac{\ln 250}{\ln 2} = 7.966 \Longrightarrow n = 8$$

# Need For Data Acquisition

- There are many applications where it is necessary to know, simultaneously, the measured values of several variables associated with a particular process, machine or situation.

- Examples are measurements of temperature measurements at different points in a nuclear reactor core, and components of velocity and acceleration for an aircraft.

Instrumentation

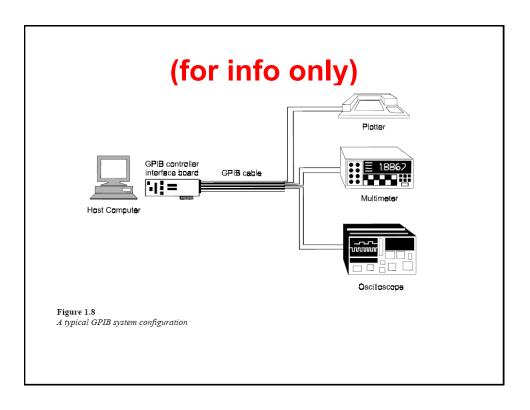

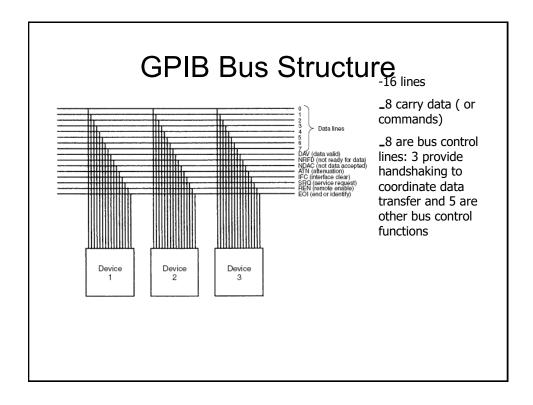

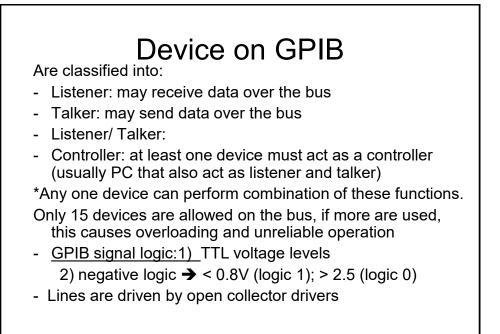

# 1.3.4 IEEE-488 (GPIB) remote programmable instruments

- The communications standard now known as GPIB (General Purpose Interface Bus), Was originally developed by Hewlett-Packard in 1965 as a digital interface for interconnecting and controlling their programmable test instruments.

- Originally referred to as the Hewlett Packard Interface Bus (HPIB), its speed, flexibility and usefulness in connecting instruments in a laboratory environment led to its widespread acceptance, and finally to its adoption as a world standard (IEEE-488).

- Since then, it has undergone improvements (IEEE-488.2) and SCPI (Standard Commands for Programmable Instruments), to standardize how instruments and their controllers communicate and operate.

- Evolving from the need to collect data from a number of different stand-alone instruments in a laboratory environment, <u>the GPIB is a high-speed parallel communications interface that allows the simultaneous connection of up to 15 devices or instruments on a short common parallel data communications bus.</u>

- Devices must be placed within 3 meters or so of the host controller/ computer

Instrumentation

- A device connected to the bus can send data (bytes) to 14 other devices on the bus

- GPIB allows data to be sent at whatever rate the devices on the bus operate.

- Hardware consideration limit the max speed of data transmission to 250 kbytes/s ( = 2 Mbits/s).

- GPIB is used to communicate with a set of instruments with the same interface for setting an automatic measurement and control system by a network of instruments

Instrumentation

| IE     | EE-4   | (for info only)<br>88 CON |                             | Pin out<br>2 |                |

|--------|--------|---------------------------|-----------------------------|--------------|----------------|

|        |        |                           | 2                           | 4            | 13             |

| Pin 1  | DIO1   | Data                      | A female IEEE-488 connector |              |                |

|        |        | input/output bit.         | Pin 15                      | DIO7         | Data           |

| Pin 2  | DIO2   | Data                      |                             |              | input/output   |

|        |        | input/output bit.         | Pin 16                      | DIO8         | Data           |

| Pin 3  | DIO3   | Data<br>input/output bit. |                             |              | input/output 1 |

| Pin 4  | DIO4   | Data                      | Pin 17                      | REN          | Remote enab    |

| гш 4   | DIO4   | input/output bit.         | Pin 18                      | GND          | (wire twisted  |

| Pin 5  | EOI    | End-or-identify.          |                             |              | with DAV)      |

| Pin 6  | DAV    | Data valid.               | Pin 19                      | GND          | (wire twisted  |

| Pin 7  | NRFD   | Not ready for             |                             |              | with NRFD)     |

|        |        | data.                     | Pin 20                      | GND          | (wire twisted  |

| Pin 8  | NDAC   | Not data                  |                             |              | with NDAC)     |

|        |        | accepted.                 | Pin 21                      | GND          | (wire twisted  |

| Pin 9  | IFC    | Interface clear.          |                             |              | with IFC)      |

| Pin 10 | SRQ    | Service request.          | Pin 22                      | GND          | (wire twisted  |

| Pin 11 | ATN    | Attention.                |                             |              | with SRQ)      |

| Pin 12 | SHIELD |                           | Pin 23                      | GND          | (wire twisted  |

| Pin 13 | DIO5   | Data                      |                             |              | with ATN)      |

|        |        | input/output bit.         | Pin 24                      | Logic grou   | und            |

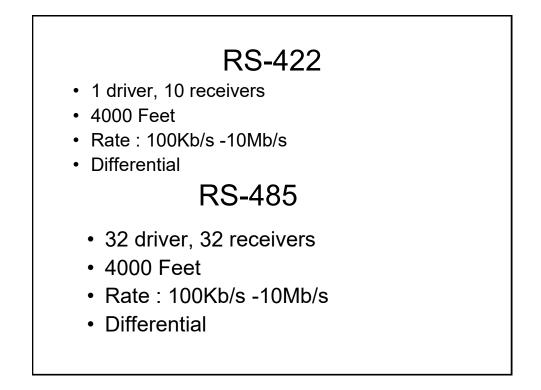

# Other Interfaces measurement systems Serial Interface is often used when a single instrument is to be connected to a PC over long distance RS232 was originally developed in 1960s and it is slow, not flexible and rarely used on instruments, however it is used for specific applications such as reading in data from remote dc sensors and sending data to loggers Other more modern, serial asynchronous data transmission protocols include RS422, RS423, RS449, RS485 and USB RS stands for recommended standard

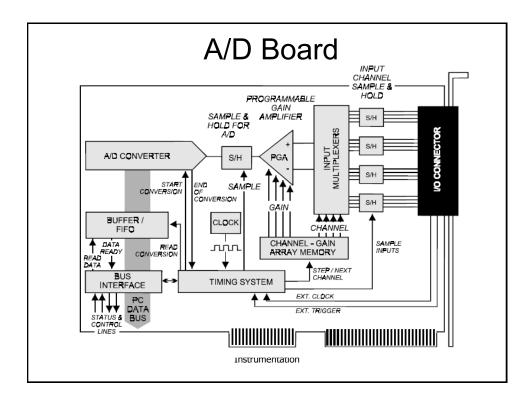

- Total throughput, for multiple conversions on different channels, is often increased by overlapping parts of this cycle.

- For example:

While the A/D converter is busy converting the S/H output, the next channel/gain pair can be output to the multiplexer and PGA, so that their settling and delay times are overlapped with the A/D conversion time.

• The timing circuitry may also include a block-sampling mode, which allows blocks of samples to be collected at regular intervals at the A/D board's maximum sampling rate.

- These techniques are discussed in the following sections:

- Continuous channel scanning

- Simultaneous sampling

- Block mode operations

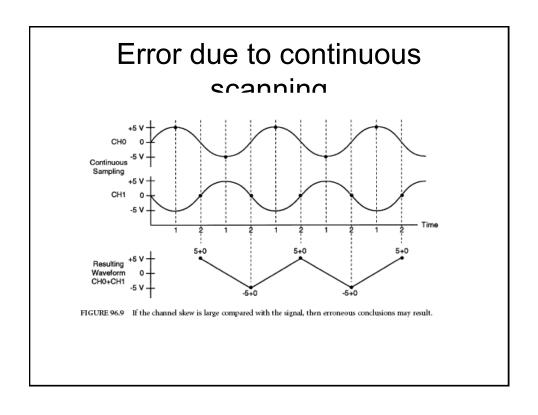

#### **Continuous channel scanning**

- The method of sampling that facilitates the connecting of the required input channel to the A/D converter at a constant rate is known as continuous channel scanning.

- Continuous channel scanning allows channels to be sampled in a pre-determined and arbitrary order (e.g. channel 5, channel 1, channel 11), as well as at different sampling rates.

- An example of this would be the sampling of three channels in the following order (channel 5, channel 1, channel 11, channel 1). Channel 1 is being sampled at twice the rate as channels 5 & 11, which for an A/D board with throughput of 100 kHz represents a sampling rate of 50 kHz.

- Channels 5 & 11 are sampled at 25 kHz.

- There are two methods of continuous channel scanning, either under software control or by on-board hardware control using Channel Gain Array.

### Important

- Maximum throughput per channel = Total throughput / # of channels

- For example if you wish to sample 4 channels at 50 kHz each, you need a board with throughput of 200 kHz